在科技界追求极致AI运算性能的浪潮中,数据传输的瓶颈日益显著。为此,台积电的欧洲OIP论坛公布了一项重大技术展示,世芯(Alchip)与Ayar Labs联手推出一款完全集成的封装内光学I/O引擎,这项解决方案采用台积电的Compact Universal Photonic Engine(COUPE)平台,为下一代AI芯片带来了革命性的光学连接能力。

让中小企业轻松拥有光学I/O以填补市场空白根据公布数据显示,这套全新的光学I/O解决方案具有极高的市场意义。台积电于2024年推出COUPE框架时,主要目标客户是大型芯片开发商,例如AMD或Nvidia,这些公司有能力自行设计电子集成电路(EIC)和光子集成电路(PIC),再由台积电负责制造。

然而,许多定制化加速器的设计者通常缺乏垂直集成资源,他们不像Nvidia那样能通过其NVL72、NVL144和NVL576等平台,控制从计算到扩展连接的整个技术堆栈。这些设计者更倾向于最大限度地授权现有技术,然后专注于开发使自家解决方案与众不同的知识产权(IP)。

世芯与Ayar Labs共同发布的这个产品化(production-ready)光学子系统,正是为了解决这一资源门槛。它使较小的芯片设计商能够相对轻松地为其芯片添加光学连接能力,而无需像自行开发那样预先投入数千万美元的高昂成本。

这项解决方案的关键在于其精密的协同封装设计,它结合了Ayar Labs的硅光子TeraPHY集成电路(IC)、世芯的电气界面晶粒、以及一个可拆卸的光纤连接器。具体而言,这个光学I/O子系统是一个三芯片小芯片(chiplet)协同封装架构,包含以下核心组件:

在性能方面,世芯与Ayar Labs的集成式光学I/O展现了极致的扩展能力(extreme scale-up)。该子系统可完成高达100 Tb/s的带宽,并且支持每个加速器设备拥有超过256个光学端口。这种连接轨模使得数百个处理器能够跨越多个机架进行连接,并能被操作为单一的大型处理器。

另外,该系统还针对不同的延迟需求,该光学子系统提供了两种主要的连接选项。首先是PAM4 CWDM,这种模式的跳跃延迟(per hop)约为100-200奈秒,位元错误率(BER)小于10⁻⁶。另外,提供DWDM快速跟随器(fast-follower)部分,这种模式的延迟极低,跳跃延迟仅需20–30奈秒,位元错误率小于10⁻¹²。因此,除了处理器之间的超大规模互联外,可以预见的世,该解决方案将能应用于内存扩展上。

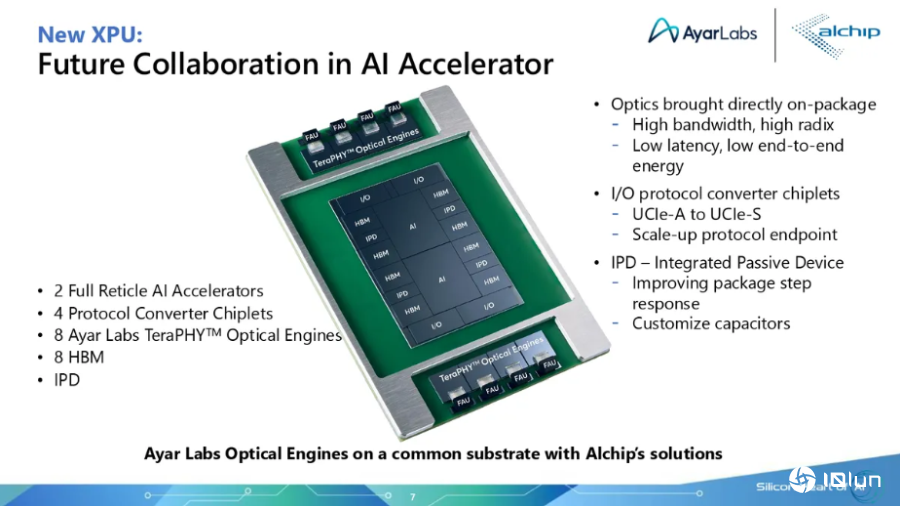

参考设计展示多场景应用为了具体展示该技术的集成潜力,相关的参考设计展现了高度复杂的系统配置。该设计包括两块全光罩加速器晶粒、八个HBM(高带宽内存)堆栈、四个协议转换器小芯片,以及八个Ayar Labs TeraPHY光学引擎。所有这些组件都安装在一个基板上,并集成了用于确保电源完整性的被动组件。

世芯的系统图也详细展示了该平台可应用的多种连接场景,涵盖了XPU(通用处理器)至XPU、XPU至交换机、以及交换机至交换机的互联。这些应用场景表明,该解决方案不仅限于芯片内通信,更能有效地创建起具备高带宽、低延迟和高能源效率的机架级甚至多机架级连接能力,甚至能实现光学内存扩展。

整体来说,通过采用以小芯片形式销售的世芯子系统,AI加速器的开发商将能获得过去只有少数顶级公司才有能力自行开发的超高带宽连接方案。这项技术的普及,将加速整体AI运算硬件生态系统的发展与创新。

(首图来源:shutterstock)

晋ICP备17002471号-6

晋ICP备17002471号-6